Flip-flop yra terminas, kuris patenka į skaitmeninę elektroniką, ir tai yra elektroninis komponentas, naudojamas vienam informacijos bitui saugoti.

Diagraminis „Flip Flop“ vaizdavimas

- Kadangi „Flip Flop“ yra nuosekli grandinė, jo įvestis pagrįsta dviem parametrais: vienas yra srovės įvestis, o kitas – ankstesnės būsenos išvestis.

- Jis turi du išėjimus, abu papildo vienas kitą.

- Jis gali būti vienoje iš dviejų stabilių būsenų – 0 arba 1.

Pagrindinė „Flip Flop“ schema

Kas yra T Flip Flop?

- T flip flop arba, tiksliau, yra žinomas kaip Toggle Flip Flop, nes jis gali perjungti savo išvestį priklausomai nuo įvesties.

- T čia reiškia Perjungti .

- Perjungimas iš esmės rodo, kad bitas bus apverstas, ty nuo 1 iki 0 arba nuo 0 iki 1.

- Čia tiekiamas laikrodžio impulsas, skirtas valdyti šį šnipą, taigi, tai yra laikrodis.

„T Flip Flop“ konstrukcija

T flip galime sukurti trimis būdais, būtent:

- Naudojant SR Flip Flops.

- Naudojant D Flip Flops.

- Naudojant JK Flip Flops

T Flip Flop konstravimo būdai

Pažiūrėkime, kaip sukurti T Flip Flop naudojant SR Flip Flops, kuriems reikia 2 AND vartų ir 2 NOR vartų, kaip parodyta žemiau:

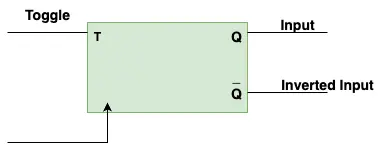

Pagrindinė „T Flip Flop“ blokinė schema

Čia blokinėje diagramoje yra perjungimo ir laikrodžio įėjimai, Q ir Q yra papildomi įėjimai.

„T Flip Flop“ veikimas

1 atvejis : Tarkim, T = 0 ir laikrodžio pulsas yra aukštas y., 1, tada abiejų, AND vartų 1, IR vartų 2 išvestis bus 0 , vartai 3 produkcija bus K ir panašiai vartai 4 produkcija bus Q' taigi ir Q, ir Q’ reikšmės yra tokios pat kaip ir ankstesnė, o tai reiškia Laikykite būseną .

2 atvejis : Tarkim, T=1 , tada abiejų IR vartų 1 išvestis bus (T * laikrodis * Q) , ir kadangi T ir laikrodis yra 1, tada IR vartų 1 išvestis bus tokia K , ir panašiai bus AND vartų 2 išvestis (T * laikrodis * Q') t.y., Q' . Dabar bus 3 vartų išėjimas (Q'+Q)' ir tarkime, kad Q' yra nulis, tada 3 vartų išėjimas bus (0+Q)' tai reiškia Q' ir panašiai bus vartų 4 išėjimas (Q+Q')' ir kadangi Q' yra nulis, tai 4 vartų išvestis bus Q', o tai reiškia 0 nes Q' yra nulis. Taigi šiuo atveju galime sakyti, kad išvestis persijungia, nes T=1 .

„T Flip Flop“ tiesos lentelė

- Čia T yra perjungti įvestis, Q yra esamos būsenos įvestis, Qt+1 yra kitos būsenos išvestis.

- Iš čia matome, kad kai perjungimas (T) yra 0, kitos būsenos išvestis (Qt+1) yra tokia pati kaip dabartinės būsenos įvestis (Q).

- Kai perjungimas (T) yra 1, kitos būsenos išvestis (Qt+1) bus esamos būsenos įvesties (Q) papildymas, o tai reiškia, kad jis perjungiamas.

Charakteristinė lygtis

- Charakteristinė lygtis mums nurodo, kokia bus kita šlepetės būsena dabartinės būsenos atžvilgiu.

- Norint gauti būdingą lygtį, sudaromas K-Map, kuris bus parodytas taip:

- Jei išspręsime aukščiau pateiktą K-Map, charakteristikos lygtis bus tokia Q(n+1) = TQn’ + T’Qn = T XOR Qn

Sužadinimo lentelė

Sužadinimo lentelė iš esmės pasakoja apie sužadinimą, kurio reikia, norint pereiti iš dabartinės būsenos į kitą.

- Čia, kai T yra 0, Qt+1 yra toks pat kaip įvestis Q.

- Ir kai T yra 1, Qt+1 yra Q įvesties papildymas.

„T Flip Flop“ programos

Skaitmeninėje sistemoje yra daug „T Flip Flop“ programų, kurios išvardytos toliau:

- Skaitikliai : T Šlepetės, naudojamos skaitikliuose. Skaitikliai skaičiuoja įvykių, įvykusių skaitmeninėje sistemoje, skaičių.

- Duomenų saugykla : T Šlepetės, naudojamos atminčiai sukurti, kuri naudojama duomenims saugoti, kai maitinimas išjungtas.

- Sinchroninės loginės grandinės : T flip-flops gali būti naudojamas sinchroninėms loginėms grandinėms įdiegti, tai yra grandinės, kurios atlieka operacijas su dvejetainiais duomenimis pagal laikrodžio signalą. Sinchronizuojant loginės grandinės operacijas su laikrodžio signalu naudojant T flip-flops, grandinės elgesys gali būti nuspėjamas ir patikimas.

- Dažnio padalijimas : Jis naudojamas laikrodžio signalo dažniui padalyti iš 2. Flip-flop perjungs savo išvestį kiekvieną kartą, kai laikrodžio signalas pereis iš aukšto į žemą arba žemą į aukštą, todėl laikrodžio dažnis dalijasi iš 2.

- Pamainų registrai : T flip-flops gali būti naudojami poslinkių registruose, kurie naudojami dvejetainiams duomenims perkelti viena kryptimi.

Išvada

Šiame straipsnyje mes pradedame nuo šlepečių pagrindų, kas iš tikrųjų yra šlepetės, o tada aptarėme „T Flip Flops“ – tris du būdus, kuriais galime sukurti „T Flip Flop“, tai yra pagrindinė blokų schema, „T Flip Flop“ veikimas. , tai tiesos lentelė, charakteristikų lygtis ir sužadinimo lentelė, o pabaigoje aptarėme T Flip Flops pritaikymą.